臺版晶片法 研發經費門檻 擬訂50~100億

產創條例第10條之2三大門檻與外界意見

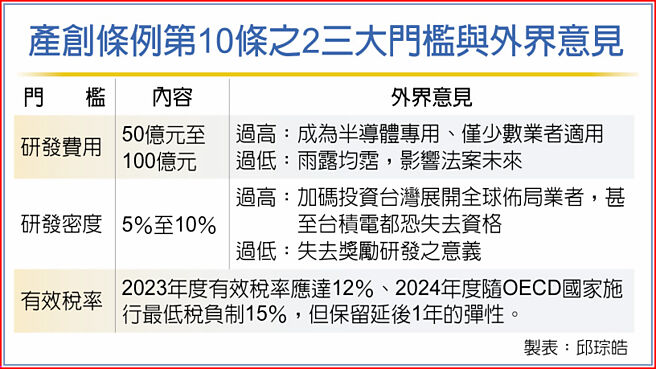

臺版晶片法案的產創條例10條之2已完成三讀,研發費用、研發密度、有效稅率訂爲適用優惠減稅的三大必備門檻,其中研發費用更連動研發密度。據透露,研發經費門檻將訂在50億至100億元,研發密度則會落在5%至7%之間。

據瞭解,財經兩部正爲此角力,也對定義及門檻傷透腦筋,深怕門檻訂太高、變成臺積電獨享,又怕門檻訂得太低、變成家家有獎,兩者都失去鼓勵意義。加上,財長未補實,督導賦稅的次長李慶華及賦稅署長許慈美二人13日雙雙屆齡退休,財經兩部無法快速展開研商。經濟部盼在3~4月內完成子法訂定,儘快公告上路。

知情官員透露,雖然研發費用、研發密度尚未定案,但先前財政部擬訂在100億,如此只有臺積電、聯發科、聯詠等6至7家業者符合條件。經濟部極力爭取後,財政部同意讓步,初步敲定研發費用門檻將訂在50億至100億元間,倘若門檻降低至50億元,包括聯電、日月光、南亞科、羣聯、瑞昱等近15家業者都可進安全名單。

第一個「研發費用」恐刷掉9成科技業者,而第二門檻「研發密度」是連動的,官員預期,恐怕再刷掉部分業者。「研發密度」是指研發支出佔營收淨額之比率,目前製造業平均爲3.2%,原本財政部有意訂在8%左右,但臺積電合併營收破2兆,未來幾年還會不斷長胖,其研發密度約達7~8%,一旦營收成長恐難達研發密度門檻,因此兩部會初步擬將研發密度比率訂在5%至7%。

至於有效稅率門檻,2023年應達12%,2024年審酌OECD全球企業最低稅負制情形調整緩衝一年,2025年起一律調整至15%。

外界擔心,產創10條之2會變成半導體產業或少數業者獨享之法案。經濟部強調,適用要件規模與相關名詞定義在子法訂定,也會參考國內外產業發展狀況、主要上市櫃公司研發經費及產業研發密度,並蒐集產業界意見及聽取產官學研專家意見來訂定。

產創條例第10條之2符合適用要件者,可享有前瞻創新研發投資抵減,當年度抵減率爲25%;購置用於先進製程之設備投資抵減,當年度抵減率爲5%,且支出金額無上限;二者合計抵減稅額不得超過當年度應納營所稅額50%。